深圳先进院提出新型高效加法器和乘法器设计方案

近日,中国科学院深圳先进技术研究院医工所黄明强博士团队与新加坡南洋理工大学合作,在新兴计算领域知名期刊IEEE Transactions on Emerging Topics in Computing上发表了题为Efficient Ternary Logic Circuits Optimized by Ternary Arithmetic Algorithms的研究。该研究针对高能效计算基础问题,提出一种基于多状态编码的新型计算电路设计方案,为大算力、低功耗、高密度计算提供了一条全新的研究思路。本研究中,深圳先进院访问学生赵广超、深圳先进院已毕业硕士生曾志威为共同第一作者,黄明强博士为通信作者,中国科学院深圳先进技术研究院为通讯单位。

在现代电子计算机系统中,任何复杂的计算任务最终都可以被分解为一系列的加法和乘法操作,因此基础加法器和乘法器的性能和效率对整个计算系统的性能至关重要。

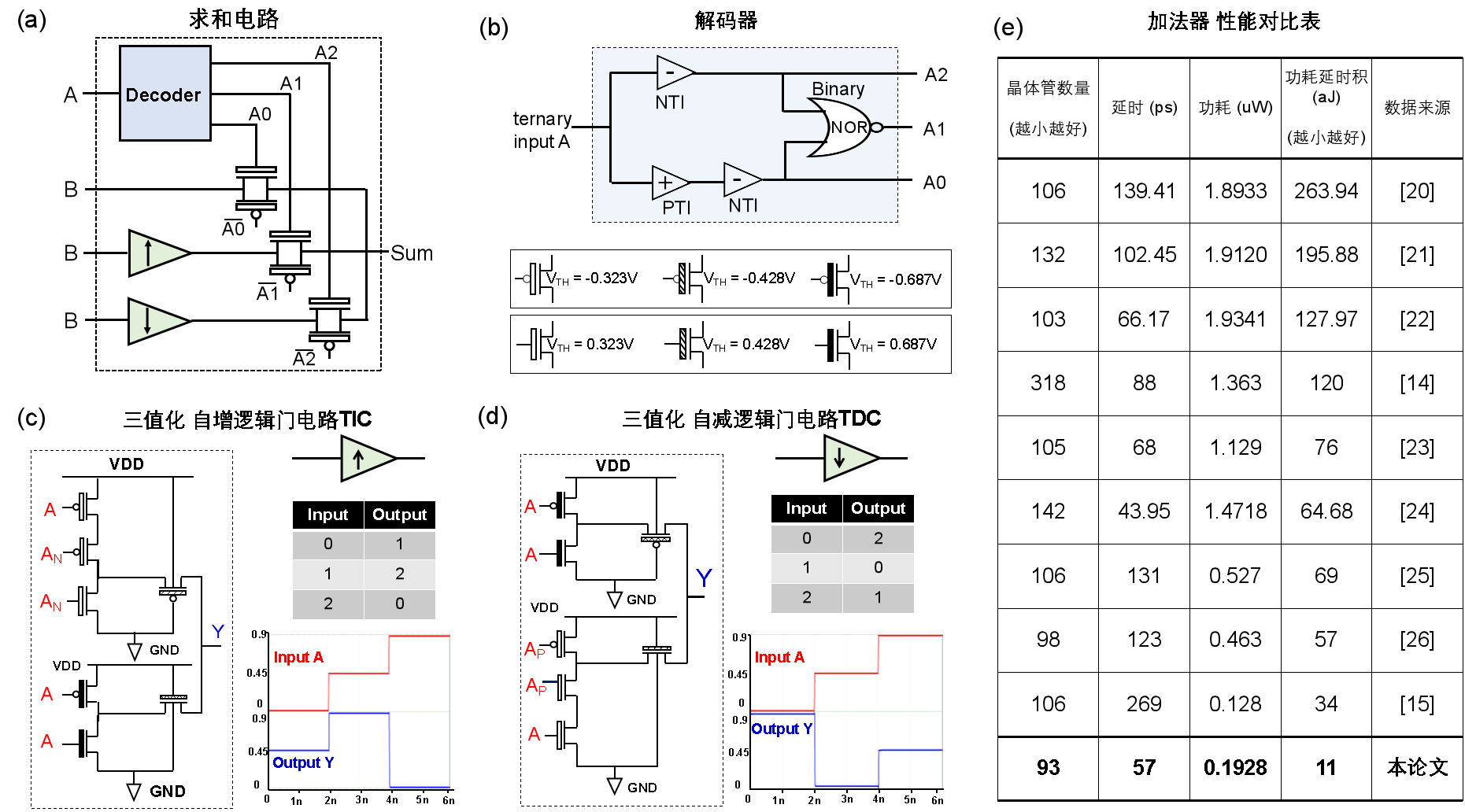

近年来,三值计算和三值逻辑电路因其比二进制硬件系统更高的信息密度而受到广泛关注。在这项工作中,我们提出了基于算法优化的高效的三值逻辑计算电路,包括三值逻辑加法器和乘法器等。本研究创新性地通过利用三值算术算法来优化电路设计,进而实现了比以往研究更优秀的设计效果。例如,我们设计了三值增量循环门(TIC)和三值递减循环门(TDC)。以TIC为例,当输入为0时,其输出为1;当输入1时,其输出为2;当输入为2时,其输出为0。这样的算法操作与加法的计算过程十分契合,因此可以引入到加法器电路种。我们利用多阈值晶体管作为基本单元,通过不同阈值的组合,实现了三值化的逻辑状态。随后我们设计了可稳定工作、且静态工作电流极低的TIC和TDC逻辑门。最终,我们结合现有多值逻辑电路的解码码-计算-编码的设计思路,实现了高效的加法器设计。

此外,三值逻辑中拥有大量的状态冗余,我们利用等价变换的方法可以实现对三值布尔真值表的优化与简化,进而能降低电路的复杂度。通过以上方案,我们设计的加法器和乘法器相较于以往的方案,晶体管使用数量、功率延迟积(PDP)都得到了显著改善,在0.5 GHz下实现具有11 aJ PDP的非平衡三值全加法器仅涉及93个晶体管,这两者都是迄今为止报道的文章中最低的。

最后,我们利用工业级180nm的硅晶体管工艺库对上述方案做了验证。实验显示,采用现有的硅器件工艺,利用多阈值器件的组合,也能完整实现上述三值化逻辑计算的功能。也即三值化逻辑电路可以利用硅工艺进行规模化量产,为其实际应用奠定了基础。

图1:本论文提出的新型加法器结构和性能对照表

图2:多值逻辑计算方案在硅基180nm工艺下的仿真验证结果