深圳先进院处理器芯片性能大数据研究获进展

7月18日晚,国际体系结构领域的CCF A类会议MICRO2018(IEEE/ACM International Symposium on Microarchitecture)评审结果揭晓,中国科学院深圳先进技术研究院数字所异构智能计算中心硕士生吕依蓉和孙斌合作的论文Counter Miner: Mining Big Performance Data from Hardware Counters被录用为长文(双栏14页)。

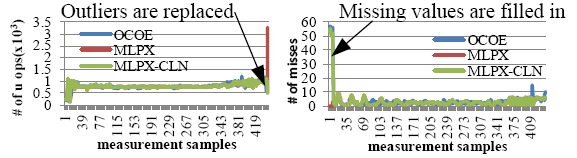

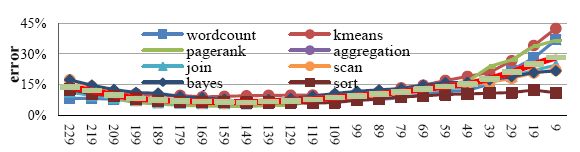

该工作提出了处理器芯片性能大数据的概念,并对其中的关键技术进行了深入研究。首先,处理器芯片以高效的方式产生的性能数据包含许多错误,论文全面观察了这些性能数据的分布,根据分布设计了基于线性回归的错误清除方法。实验结果显示,该方法能将错误率从28%降低到7%。在此基础上,论文量化分析了性能事件的重要性和事件之间的交互性,并总结出了六条规律。最后,论文还设计了一种真实的场景,即通过性能大数据挖掘来高效优化内存计算程序的性能,其优化效率比传统方法高出4倍。论文所研究的方法还可以被用在许多其他的方面,如处理器芯片体系结构性能优化、能耗优化、编译器优化、任务调度优化、应用程序性能优化等。

MICRO会议创办于1968年,是由美国电气电子工程师学会(Institute of Electrical and Electronics Engineers)、美国计算机学会(Association for Computing Machinery)联合主办的体系结构领域的顶级会议,致力于讨论和传播处理器微体系结构的创新,现代处理器中多种广为使用的技术来自于MICRO会议文章。参会对象包括微体系结构、编译器、芯片、计算机系统等领域的研究人员或学生。2018年的MICRO会议将于10月20-24日在日本福冈召开。此前,近20年来中国大陆科研院所被该会议录用的论文不超过10篇。

左:时间序列中的异常值被正常值替换;右:时间序列中的缺失事件被正确填补

模型精度随处理器性能事件个数的变化趋势